Phased-Array Radar Transceiver Octal 14-bit 5 Gsps ADC Electronic Warfare ESM /ECM

AV 145 3U VPX ZYNQ Ultrascale+ RFSoC Octal 14-bit 9.85 Gsps DAC Conduction or Air-Cooled

# Applications

Phased-Array Radar Transmitter / Receiver Electronic Warfare ESM /ECM **Broadband Communication**

## **Features**

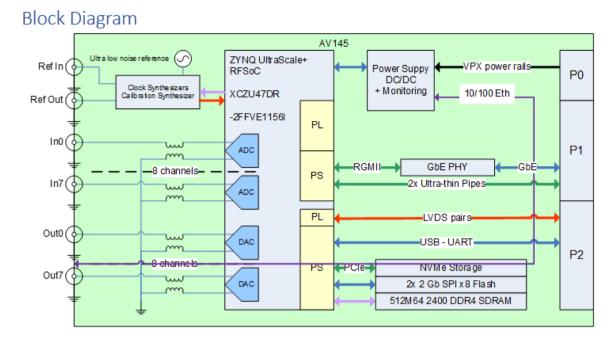

8 channels 5 Gsps 14-bit ADC 8 channels 9.85 Gsps 14-bit DAC Configurable DDC and DUC 2 Ultra Low jitter clock synthesizer External or internal sampling clock reference User programmable Xilinx® ZYNQ® Ultrascale+™ ZU47DR RFSoC 1x 64-bit 4GBytes DDR4 2400 SDRAM 1x 128GBytes NVMe embedded SSD 3U OpenVPX standard compliant

## Specifications

## Form Factor

3U VPX Air-cooled Vita 48.1, pitch 1.0" 3U VPX Conduction cooled Vita 48.2, pitch 1.0"

## **VPX** Profile

SLT3-PAY-2F2U-14.2.3

## Analog Input/Output

Input coupling: AC Full power bandwidth: 100MHz to 6 GHz Full scale: +9 dBm Output coupling: AC Full power bandwidth: 100MHz to 6 GHz Full scale: -5 dBm Impedance: 50 Ohm Connectors: SMPM

## Analog-Digital Conversion

Eight channels, up to 5Gsps Resolution: 14 bit Sampling Performances at 5Gsps NSD: -150 dBFS/Hz at -10dBFS at 3.5GHz HD2/HD3: -68 dBFS at -10dBFS at 3.5GHz IMD3: -73 dBFS at -7dBFS at 3.5GHz Configurable DDC

## **Digital-Analog Conversion**

Eight channels, up to 9.85Gsps Resolution: 14 bits Sampling Performances at 9.85Gsps NSD: -165 dBFS/Hz at 0dBFS at 3.5GHz HD2/HD3: -60 dBFS at 0dBFS at 3.5GHz IMD3: -68 dBc at -16dBFS at 3.5GHz Configurable DUC

## Clock

External or internal sampling clock reference External reference Frequency: 10MHz to 200MH Impedance: 50 Ohm Connectors: SMPM Two Ultra-low jitter clock synthesizer

## Memory

One banks 64-bit 4GBytes DDR4 2400 SDRAM Two 2 Gbit QSPI FLASH memory One 128 GBytes NVMe SSD

## **Operating Temperature**

Air-cooled EAC4, 0°C to +55°C Conduction-cooled ECC3, -40°C to 70°C

## **VPX** interface

P1:

Data plane: two fat pipes supporting PCIE GEN3 Control plane: two ultra-thin pipe CPutp to PS supporting 1 Gbps SGMII User defined: ultra-thin pipes UART and USB2.0, thin pipe for 1000BASET-T P2:

18 LVDS differential pairs, configurable as 36 single ended LVCMOS

#### **Operating Temperature**

Air-cooled EAC4, 0°C to +55°C Conduction-cooled ECC3, -40°C to 70°C

#### Power dissipation

+12V: 7.6 A max (91W) +5V : 0.5A max (2.5W) +3.3VAUX: 0.6A max (2W)

## Weight

Air cooled : 630g Conduction cooled : 700g

#### **Board Support Package**

FPGA example design SW API and examples, Windows 10 64-bits / Linux 64-bits User manuals Quick start guide

#### Ordering informations

| Part    |            | AV145 | - | С  |

|---------|------------|-------|---|----|

| Number  |            |       |   |    |

| Cooling | Air        |       | - | AS |

|         | Conduction |       | - | CS |

#### CONTACT : sales@apissys.com

www.apissys.com